L’International Solid-State Circuits Conference (ISSCC), che si tiene ogni anno in febbraio a San Francisco, è un forum internazionale dedicato alla presentazione di studi teorici e di realizzazioni pratiche nel campo dei circuiti integrati, e in particolare dei microprocessori e dei System-on-Chip (SoC). Nata nel 1954 per iniziativa dell’Institute of Radio Engineers (IRE) e dell’American Institute of Electrical Engineers (AIEE) e subito connotata da una valenza internazionale, la Conference è oggi un’emanazione dallo IEEE (Institute of Electrical and Electronics Engineers), l’ente che nel 1963 ha fuso IRE e AIEE diventando in cinquant’anni, con 430 mila membri tra ingegneri e ricercatori in 160 paesi, il referente mondiale del settore.

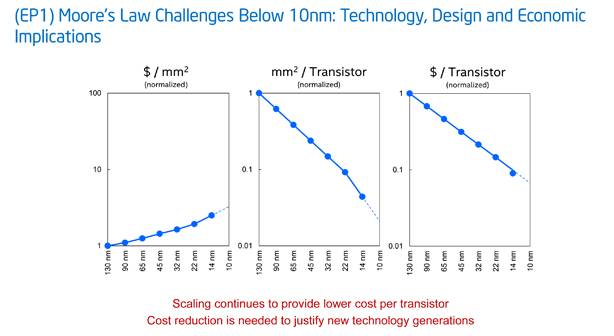

Figura 1 – Nei grafici le proiezioni dell’’andamento di costi, densità e costo per componente oltre il limite dei 14 nanometri. Fonte: Intel. Clicca per ingrandire

Figura 1 – Nei grafici le proiezioni dell’’andamento di costi, densità e costo per componente oltre il limite dei 14 nanometri. Fonte: Intel. Clicca per ingrandireQuest’anno la ISSCC ha celebrato un anniversario speciale: il cinquantenario della “Legge di Moore”. Fu infatti nel febbraio 1965 che Gordon Moore, allora capo della ricerca in Fairchild ma che nel 1968 avrebbe, con Robert Noyce, fondato la Intel, ebbe a scrivere in un articolo che le prestazioni dei processori e il relativo numero dei transistor sarebbero raddoppiati ogni anno. Corretto dallo stesso Moore in 18-24 mesi l’arco temporale, questa previsione si è rivelata sorprendentemente esatta nel tempo. E proprio oggi, cinquant’anni dopo, Intel ha scelto l’ISSCC per fare il punto sugli annunci, anticipati ai primi di gennaio al Consumer Electronic Show di Las Vegas, che ne riaffermano la validità. Si tratta della presentazione dei primi circuiti realizzati in tecnologia Cmos a 14 nanometri e degli studi per lo sviluppo di tecnologie di produzione che portano il limite di miniaturizzazione verso i 10 nanometri e oltre.

Parliamo prima di quello che già esiste, cioè dei chip a 14 nm. Su questa tecnologia Intel lavorava da tempo e nell’agosto 2013 aveva dichiarato (vedi questo articolo) di prevederne entro il 2014 l’applicazione al progetto Broadwell (processori grafici parte della famiglia Xeon) e a una nuova generazione dei SoC Atom. Con un lieve ritardo creato da “inattese difficoltà delle quali faremo tesoro per accelerare gli sviluppi futuri”, come ha detto Mark Bohr, Intel Senior Fellow Logic Tech Development in una teleconferenza per la stampa specializzata, l’obiettivo è stato centrato e la produzione industriale è in atto. Non solo: oggi Intel vi ha aggiunto un SoC TX dual-mode (ricetrasmittente) pensato per il promettente mercato dei dispositivi “wearable”, una Sram da 84 Mb Cmos FinFET (non planare) e un serial link da 10 Gb al secondo in tecnologia Cmos Tri-Gate, sempre a 14 nm. Va detto che anche Samsung lavora in tecnologia a 14 nm, ma Intel pare oggi più avanti nella miniaturizzazione dei componenti (nelle celle Sram ha raggiunto l’incredibile limite di 0,5 nm2) ed è in grado di documentarne i vantaggi in termini di rendimento e consumo energetico (ancora la Sram, per dire, opera a 1,5 GigaHz con solo 0,6 V).

Ma la corsa alla dimensione, letteralmente, atomica non si ferma qui. All’ISSCC Intel ha presentato dei ‘white paper’ su tecnologie che in un arco di due anni, cioè entro il 2017, permetterebbero di raggiungere e superare i 10 nm. Siamo nel campo della ricerca e si parla di nanotubi in carbonio e nanostrutture di grafene, ma se, come pare, il mercato continuerà a premere per sistemi sempre più compatti e sempre meno ‘energivori’ non c’è motivo di credere che ancora una volta la legge di Moore sarà rispettata.